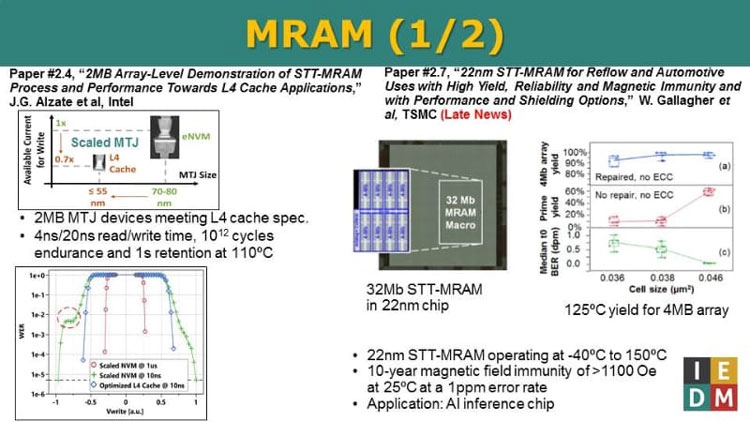

На днях в Сан-Франциско стартовала очередная годовая конференция International Electron Devices Meeting 2019. Среди многих интересных тем, поднятых на IEDM 2019, выделяется тема опытного производства магниторезистивной памяти STT-MRAM на эффекте переноса спина электрона. Свои достижения в области разработки энергонезависимой памяти следующего поколения представили компании Samsung, GlobalFoundries, TSMC и компания Intel. По мере появления новой информации мы будем раскрывать подробности с выступлений представителей компаний. Пока же мы вкратце сообщим о новом достижении Intel ― компания представила массив STT-MRAM для кеш-памяти L4.

Год назад на IEDM 2018 компания Intel рассказала о выпуске 7-Мбит массивов STT-MRAM с использованием техпроцесса с нормами 22 нм (22FFL). Новый опытный чип содержит массив STT-MRAM объёмом 2 Мбайт. Это память для встраиваемого применения, которая обещает заменить как традиционную встраиваемую NAND-флеш, так и память SRAM, если речь идёт об использовании STT-MRAM в качестве кеш-памяти процессоров и ускорителей. Впрочем, пока речь не идёт о процессорах. В Intel предлагают использовать встраиваемую STT-MRAM как кеш-память для ускорителей для задач ИИ и машинного обучения.

Представленный 22-нм 2-Мбайт блок STT-MRAM позволяет считывать данные со скоростью 4 нс и записывать их со скоростью 20 нс. Устойчивость ячеек к износу достигает 1012. Время удержания данных всего 1 секунда при температуре 110 градусов по Цельсию. Для долговременной памяти это не подходит, но для кеш-памяти окажется достаточным. Экономия по потреблению всё равно будет значительная.

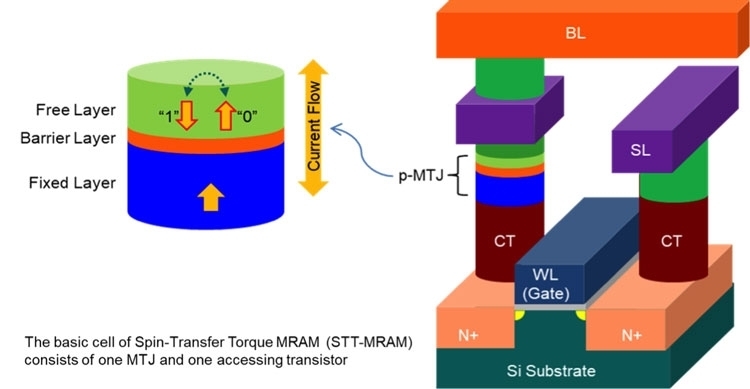

Пример строения ячейки STT-MRAM

Особенность производства памяти STT-MRAM компании Intel заключается в том, что для её выпуска достаточно не больше трёх фотошаблонов. Ячейки памяти на основе магнитных туннельных переходов изготавливаются в слое контактов и не занимают место на кристалле. На кристалле располагаются только управляющие ячейками транзисторы ― по одному транзистору на ячейку. Такие массивы хорошо масштабируются и намного плотнее, чем классическая память SRAM из 6 транзисторов на каждую ячейку.

Источник:

![Intel показала возможности суперсемплинга XeSS на практике [ВИДЕО] Intel показала возможности суперсемплинга XeSS на практике [ВИДЕО]](https://segodnya-news.ru/wp-content/uploads/2021/11/intel-pokazala-vozmozhnosti-supersemplinga-xess-na-praktike-video-400x265.jpg)

![Intel показала первый процессор Core 13-го поколения в действии [ВИДЕО] Intel показала первый процессор Core 13-го поколения в действии [ВИДЕО]](https://segodnya-news.ru/wp-content/uploads/2022/02/intel-pokazala-pervyj-processor-core-13-go-pokolenija-v-dejstvii-video-445x265.png)